# **IR3Y48A1**

# **CCD Signal Process & Digital Interface IC**

#### **DESCRIPTION**

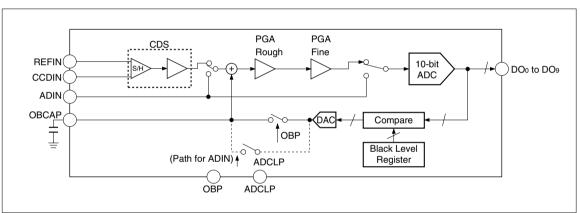

The IR3Y48A1 is a CMOS single-chip signal processing IC for CCD area sensors which includes correlated double sampling circuit (CDS), clamp circuit, programmable gain amplifier (PGA), reference voltage generator, black level detection circuit, 18 MHz 10-bit analog-to-digital converter (ADC), timing generator for internally required pulses, and serial interface for internal function control and PGA gain control.

#### **FEATURES**

• Low power consumption : 80 mW (TYP.)

Wide gain range: -1.94 to 36 dB (Gain step: 0.047 dB/step)

High speed sample-and-hold circuits: pulse width 11 ns (MIN.)

Independent CDS and PGA gain control

CDS: -1.94/0/6/12 dBPGA: 0 to 24 dB

• Black level canceler

Settling target : 16 to 127 LSB

Capable of independent input of ADC conversion clock and data output clock

Power down mode : less than 1 mW

· Built-in serial interface

• 10-bit ADC operating up to 18 MHz

- DNL: ±0.6 LSB (TYP.)

Maximum input level of CCD signals: 1.1 Vp-p

Accepts a direct signal input to ADC or PGA (input level : 1.0 Vp-p (TYP.))

Single 2.7 to 3.6 V power supply

· Package:

48-pin QFP\* (P-QFP048-0707) 0.5 mm pin-pitch

\*Contact SHARP in order to obtain the details of package dimensions of the IR3Y48A1.

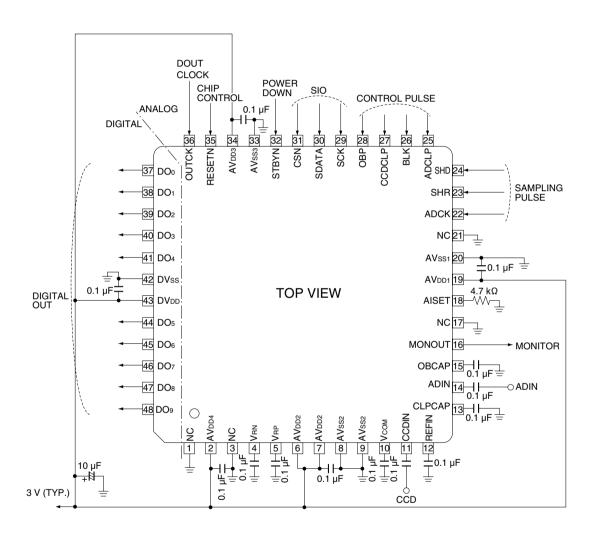

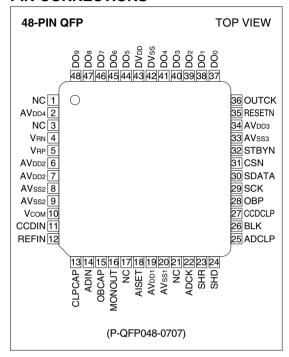

#### PIN CONNECTIONS

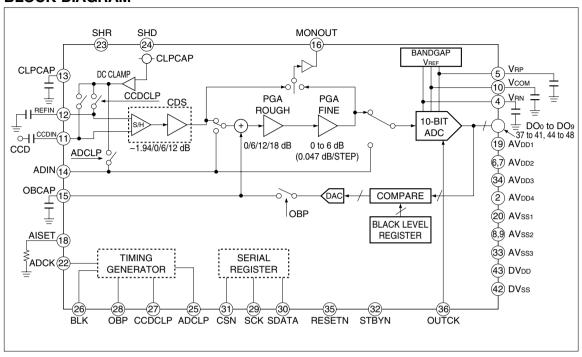

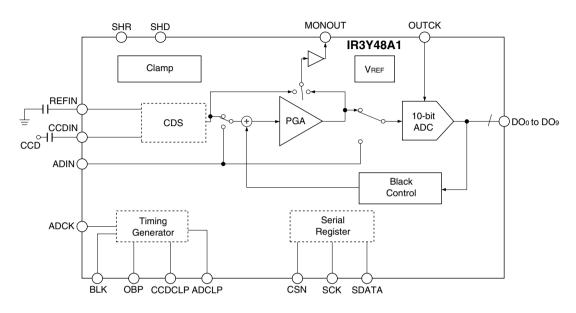

#### **BLOCK DIAGRAM**

# **PIN DESCRIPTION**

| PIN NO. | SYMBOL            | I/O | EQUIVALENT CIRCUIT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | DESCRIPTION                                                            |

|---------|-------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|

| 1       | NC                | _   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | No connection.                                                         |

| 2       | AV <sub>DD4</sub> | _   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Supply of 2.7 to 3.6 V analog power.                                   |

| 3       | NC                | -   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | No connection.                                                         |

| 4       | VRN               | 0   | V <sub>DD</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ADC internal negative reference voltage. (Connect to AVss via 0.1 µF.) |

| 5       | VRP               | 0   | THE GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ADC internal positive reference voltage. (Connect to AVss via 0.1 µF.) |

| 6       | AV <sub>DD2</sub> | _   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Supply of 2.7 to 3.6 V analog power.                                   |

| 7       | AV <sub>DD2</sub> | _   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Supply of 2.7 to 3.6 V analog power.                                   |

| 8       | AVss2             | _   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | An analog grounding pin.                                               |

| 9       | AVss2             | _   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | An analog grounding pin.                                               |

| 10      | Vсом              | 0   | V <sub>DD</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ADC internal common reference voltage. (Connect to AVss via 0.1 µF.)   |

| 11      | CCDIN             | I   | V <sub>DD</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | CDS circuit data input.                                                |

| 12      | REFIN             | I   | The second secon | CDS circuit reference input.                                           |

| 13      | CLPCAP            | 0   | VDD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Clamp level output.<br>(Connect to AVss via 0.1 µF.)                   |

| 14      | ADIN              | I   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ADIN signal input.                                                     |

| 15      | OBCAP             | 0   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Black level integration voltage. (Connect to AVss via 0.1 μF.)         |

| 16      | MONOUT            | 0   | GND GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Monitor output of CDS or PGA.                                          |

<sup>\*</sup> Internal FET gate

| PIN NO. | SYMBOL            | I/O | EQUIVALENT CIRCUIT | DESCRIPTION                                                               |

|---------|-------------------|-----|--------------------|---------------------------------------------------------------------------|

| 17      | NC                | _   |                    | No connection.                                                            |

| 18      | AISET*            | I   | ₩ VDD  W GND       | Internal analog circuit bias current input. (Connect to AVss via 4.7 kΩ.) |

| 19      | AV <sub>DD1</sub> | _   |                    | Supply of 2.7 to 3.6 V analog power.                                      |

| 20      | AVss1             | _   |                    | An analog grounding pin.                                                  |

| 21      | NC                | _   |                    | No connection.                                                            |

| 22      | ADCK              | Ι   |                    | ADC sampling clock input.                                                 |

| 23      | SHR               | I   |                    | Reference sampling pulse input.                                           |

| 24      | SHD               | I   |                    | Data sampling pulse input.                                                |

| 25      | ADCLP             | I   | VDD                | Pulse input for ADIN clamp and black calibration control.                 |

| 26      | BLK               | I   |                    | Blanking pulse input.                                                     |

| 27      | CCDCLP            | I   | <u></u>            | Clamp control input.                                                      |

| 28      | OBP               | I   | <u> </u>           | Black level period pulse input.                                           |

| 29      | SCK               | I   | GND                | Serial port clock input.                                                  |

| 30      | SDATA             | I   | GIVE               | Serial port data input.                                                   |

| 31      | CSN               | I   |                    | Serial port chip selection (active at low).                               |

| 32      | STBYN             | I   |                    | Power down control (power down at low).                                   |

| 33      | AVss3             | _   |                    | An analog grounding pin.                                                  |

| 34      | AV <sub>DD3</sub> | _   |                    | Supply of 2.7 to 3.6 V analog power.                                      |

| 35      | RESETN            | I   | V <sub>DD</sub>    | Reset signal input (reset at low).                                        |

| 36      | OUTCK             | I   | GND                | Clock input for ADC output.                                               |

\* High-Z at power down % Internal FET gate

| PIN NO. | SYMBOL | I/O | EQUIVALENT CIRCUIT | DESCRIPTION                           |

|---------|--------|-----|--------------------|---------------------------------------|

| 37      | DO0*   | 0   |                    | ADC digital output (3 state) (LSB).   |

| 38      | DO1*   | 0   | V <sub>DD</sub>    | ADC digital output (3 state).         |

| 39      | DO2*   | 0   | √ w √ r            | ADC digital output (3 state).         |

| 40      | DO3*   | 0   | <b>↑</b> □⊢ GND    | ADC digital output (3 state).         |

| 41      | DO4*   | 0   | CIND               | ADC digital output (3 state).         |

| 42      | DVss   | _   |                    | A digital grounding pin.              |

| 43      | DVDD   | _   |                    | Supply of 2.7 to 3.6 V digital power. |

| 44      | DO5*   | 0   |                    | ADC digital output (3 state).         |

| 45      | DO6*   | 0   | V <sub>DD</sub>    | ADC digital output (3 state).         |

| 46      | DO7*   | 0   | → w ⊢ r            | ADC digital output (3 state).         |

| 47      | DO8*   | 0   | THE GND            | ADC digital output (3 state).         |

| 48      | DO9*   | 0   | L                  | ADC digital output (3 state) (MSB).   |

\* High-Z at power down

NOTE: NC pins are not connected internally, but recommended to be connected to AVss.

#### **FUNCTIONAL DESCRIPTION**

### **Outline**

The configuration of the IR3Y48A1 is described below.

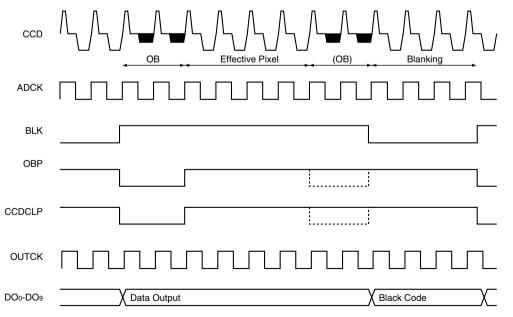

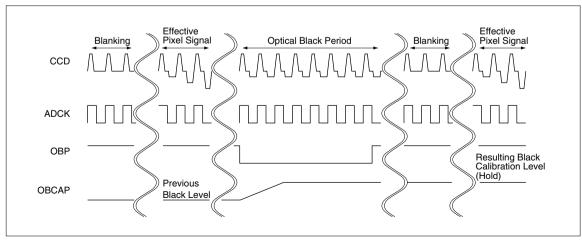

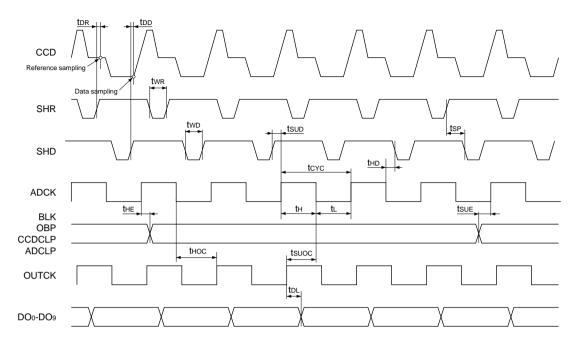

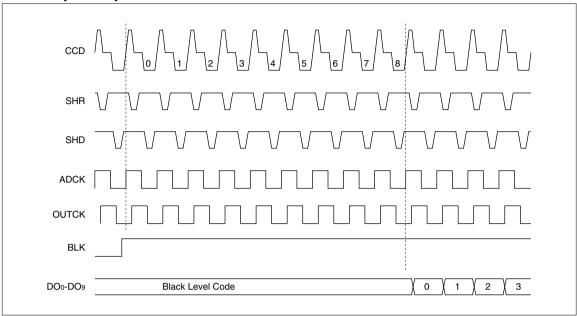

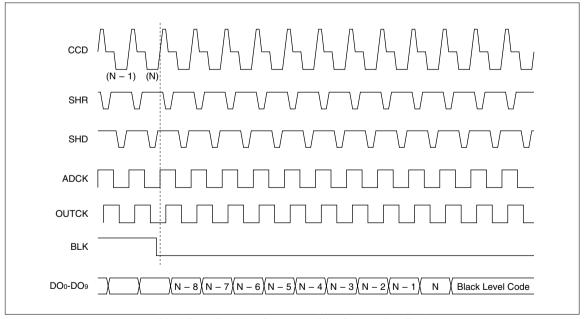

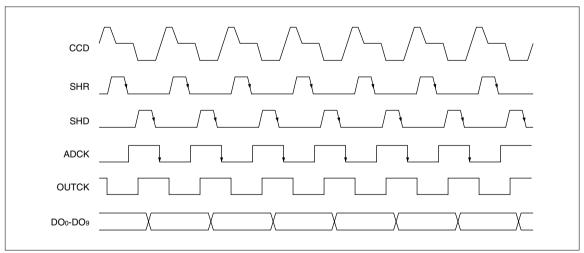

#### **GENERAL TIMING**

**NOTE:** In this chart, the cycles of the OBP and CCDCLP show the same timing. But the OBP and CCDCLP can be input at different timing.

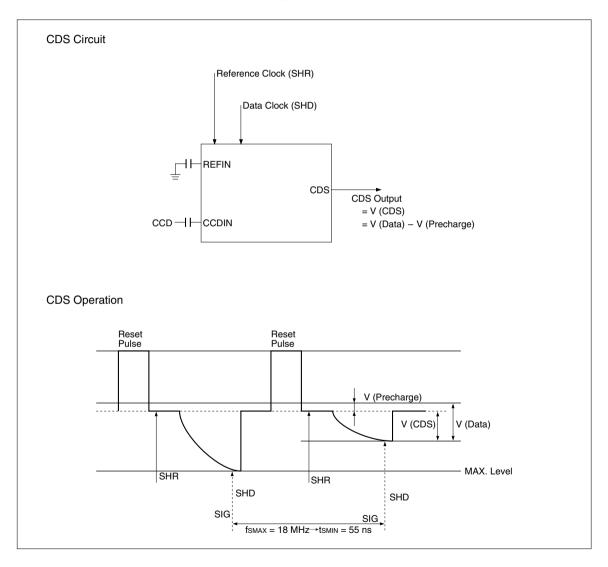

### CDS (Correlated Double Sampling) Circuit

Connect the signal from a CCD sensor to the CCDIN pin via a capacitor and connect the REFIN pin to AVss via a capacitor.

The CDS circuit holds the CCD precharge (reference) level at SHR pulse, then it samples the CCD pixel data at SHD pulse. Correlated (common) noise is removed by the subtracting

precharge level from the pixel data level.

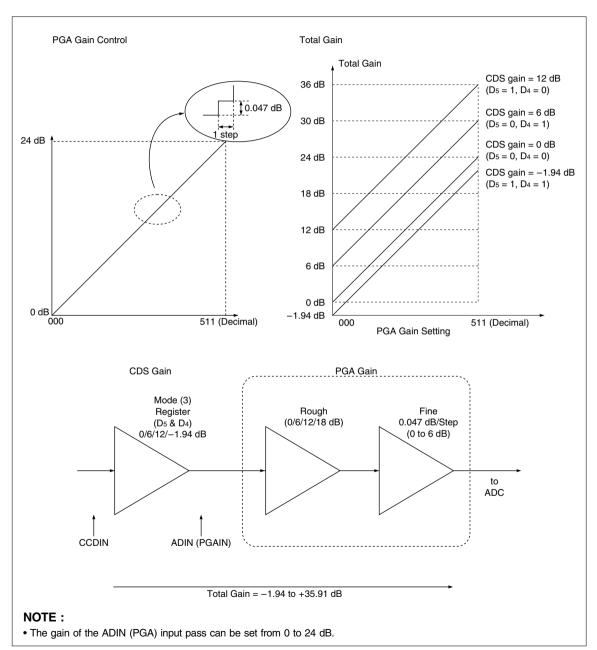

CDS can choose a gain setting from 0, 6.02, 12 or -1.94 dB (Mode (3) Register D4 & D5 bits). A CDS gain is controlled separately from a PGA gain. To reduce noise as much as possible, it is recommended to increase the CDS gain first before increasing the PGA gain.

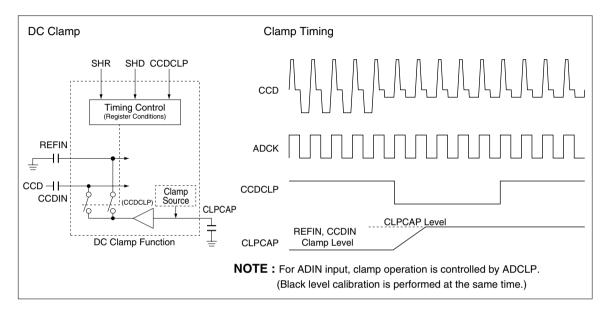

# Clamp Circuits DC CLAMP

DC level of the CCDIN/REFIN input is fixed by internal DC clamp circuit. DC level of C-coupled CCD signal at the CDS input is set to CLPCAP by

the internal DC clamp circuit.

Normally clamp switches are turned on at the black level calibration period. Place 0.1  $\mu F$  external capacitance between CLPCAP and AVss.

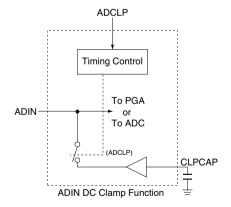

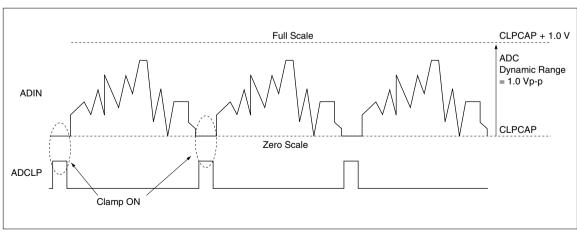

#### CLAMP OF THE ADIN SIGNAL

Clamp operation for the ADIN path is also available. Note that clamp voltage [CLPCAP] is different between CCDIN/REFIN input and the ADIN input. Clamp operation of ADIN signal can be turned off by register setting.

Clamp circuit is controlled by ADCLP signal at "ADIN signal to ADC" mode. Black level calibration circuit is also controlled by ADCLP at "ADIN signal to PGA" mode.

#### **CLAMP CONTROL**

Following items are selectable by the register setting.

- a) Clamp current [Mode (2) Register D7]

Normal or fast clamp is selectable for charge current. (Select normal clamp in general.)

- b) Clamp target [Mode (2) Register D5 & D4] Input signals (REFIN and CCDIN) to be clamped are selectable. It is also possible to turn off the clamp function.

#### ADIN DC Clamp

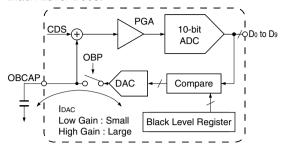

#### **Black Level Cancel Circuit**

The purpose of a black level cancel circuit is to control the DC level of the PGA input so that the ADC output code at a optical black period may correspond to the black level code set up by the register. The black level code of (1 to) 16 to 127 LSB (default: 64 LSB) is available.

A black level cancel loop is established while the OBP pin is active. In this loop, the ADC output code is compared with the black level code and the voltage of the OBCAP capacitor is controlled by the result. Thus, the OBCAP voltage settles gradually, and the signal level of the optical black period corresponds to the established value.

The charge of the OBCAP capacitor is reset under

following conditions:

- ① Set the black level reset register to "1". [Mode (1) Register D1 = 1]

- 2 Set the RESET pin to low.

- ③ Power down (by the STBYN pin or register control)

The DC clamping [CCDCLP] is allowed while the OBP pin is low.

The black level cancellation is also available in "ADIN signal to PGA" mode. (See the broken line path of "Black Level Calibration" below.) The black level cancellation is available at the ADCLP period in this mode. (That means a clamping and a black level cancelling are done simultaneously.)

**Black Level Calibration**

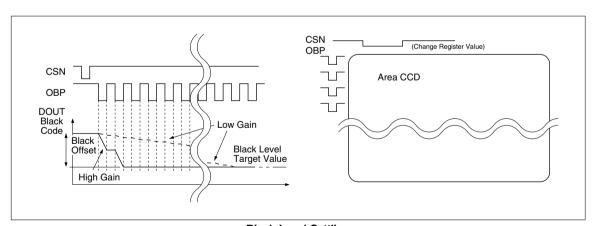

**Black Level Calibration Timing**

SHARP IR3Y48A1

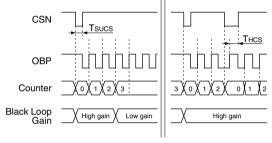

### **High-speed Black Level Cancellation**

The IR3Y48A1 has the function that settles a black level at high speed. The function that increases a settling speed in a fixed period from the access to the serial interface can become available by the register setting. This function increases the gain of the settling DAC in a fixed period, and it increases the charge/discharge current to the OBCAP capacitor.

The black level boost function is set with the Mode (3) register, D<sub>3</sub>, D<sub>2</sub>, D<sub>1</sub> and D<sub>0</sub> bits. The default setting is always low gain (D<sub>3</sub> = D<sub>2</sub> = D<sub>1</sub> = D<sub>0</sub> = 0). By setting the register D<sub>2</sub>, D<sub>1</sub> and D<sub>0</sub> bits, the gain becomes high during 1 to 7 times of OBP pulse period after any access to the serial interface. After that period, the gain returns to low.

When setting D<sub>3</sub> to "1", the gain is always high. The CSN signal becomes the starting point of the OBP pulse count.

The right figure of "Black Loop Settling Gain Boost Timing" is the timing chart when the boost control is on and the boost period is set to 3. The left figure of "Black Level Settling" below is the image of the settlement when the gain is high or low.

#### Black Level Boost

#### Black Loop Settling Gain Boost Timing

Gain boost function ON (Mode (3)  $D_3 = 1$ ) High gain for 3 pulses (Mode (3)  $D_2 = 0$ ,  $D_1 = 1$ ,  $D_0 = 1$ )

**Black Level Settling**

#### **CSN & OBP TIMING**

| PARAMETER      | SYMBOL | CONDITIONS | MIN. | TYP. | MAX. | UNIT  |

|----------------|--------|------------|------|------|------|-------|

| CSN setup time | Tsucs  |            | 0    |      |      | μs    |

| CSN hold time  | THCS   |            | 5    |      |      | clock |

#### **Gain Control Circuit**

The total gain for a CCD input signal covers from –1.94 to +36 dB.

This range consists of CDS (0/6/12/-1.94 dB), PGA

rough (0/6/12/18 dB), and PGA fine (0 to 6 dB (0.047 dB/step)). The CDS gain is controlled by a 2-bit register and the PGA gain is controlled by a 9-bit register.

**Gain Control**

SHARP IR3Y48A1

#### A/D Converter Circuit

The IR3Y48A1 integrates an 18 MHz 10-bit full pipeline A/D converter (ADC).

This ADC converts following signals:

- 1. The signal from the CCDIN input through a CDS and a PGA

- 2. The signal from the ADIN input through a PGA at the ADIN (PGA input) mode.

- 3. The signal from the ADIN input at the ADIN (ADC input) mode.

#### A/D CONVERSION RANGE

The analog input range of the ADC is determined by the internal reference voltage.

The full scale of the ADC is 1.0 Vp-p (single end).

# A/D CONVERTER OUTPUT CODE (AT MODE (1) REGISTER D5 = 1)

The format of an ADC digital output is a straight binary.

Thus, when input a zero reference voltage, the output code is "all 0", and when input a full scale voltage, the output code is "all 1".

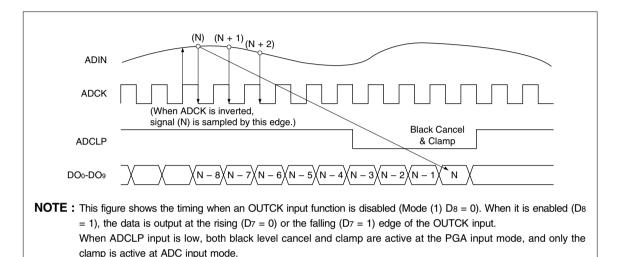

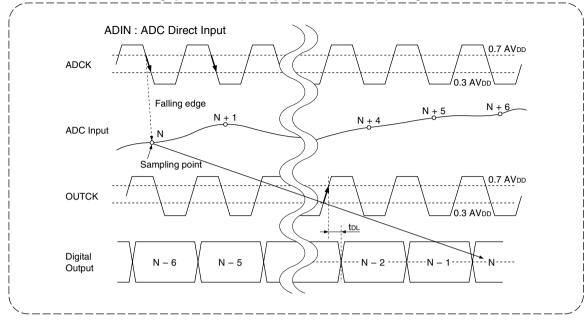

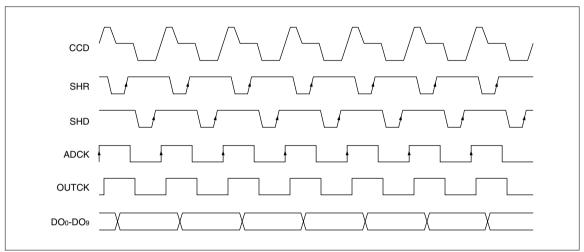

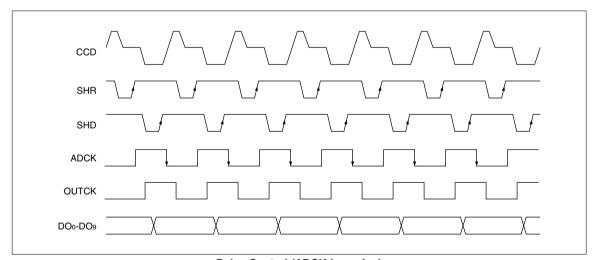

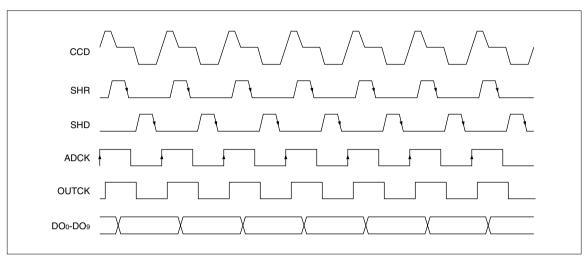

# CLOCK, PIPELINE DELAY, DIGITAL DATA OUTPUT TIMING

The ADCK input is used for an A/D conversion. The ADC input signal is sampled at the falling edge of the ADCK input and 10-bit parallel data is output at the rising edge of the ADCK input after 5.5 clocks of pipeline delay.

#### HIGH-Z CONTROL OF ADC DIGITAL OUTPUT

ADC digital outputs become High-Z under following conditions :

1) Set the ADC output bit to "1".

[Mode (1) Register  $D_2 = 1$ ]

- ② Set the SYBYN pin to low.

- (3) Set the power control bit to "1".

[Mode (1) Register  $D_0 = 1$ ]

#### ADC Data Output (Coding: Straight Binary)

| A/D INPUT  |     | D  | IGI | TAL | ΟU             | ΤPl | JT ( | OD | E  |     |

|------------|-----|----|-----|-----|----------------|-----|------|----|----|-----|

|            | MSB |    |     |     |                |     |      |    |    | LSB |

|            | D9  | D8 | D7  | D6  | D <sub>5</sub> | D4  | Dз   | D2 | D1 | Do  |

| Full scale | 1   | 1  | 1   | 1   | 1              | 1   | 1    | 1  | 1  | 1   |

| :          |     |    |     |     | :              |     |      |    |    |     |

| :          | 1   | 0  | 0   | 0   | 0              | 0   | 0    | 0  | 0  | 0   |

| :          | 0   | 1  | 1   | 1   | 1              | 1   | 1    | 1  | 1  | 1   |

| :          |     |    |     |     | :              |     |      |    |    |     |

| Zero scale | 0   | 0  | 0   | 0   | 0              | 0   | 0    | 0  | 0  | 0   |

# Miscellaneous Functions ADC DIRECT INPUT (ADIN MODE)

The direct input path to the ADC or the PGA becomes available by register setting. The selectable paths are shown below:

1. Function disable (default)

[Mode (1) Register  $D_5 = 0$ ,  $D_4 = 0$ ]

2. ADIN input to the PGA

[Mode (1) Register  $D_5 = 0$ ,  $D_4 = 1$ ]

3. ADIN input to the ADC

[Mode (1) Register  $D_5 = 1$ ,  $D_4 = don't care$ ] At the ADIN mode, the BLK, SHD and SHR inputs are ignored.

**ADIN Signal Processing (PGA Input)**

The operation at ADC direct input is shown below. Thus, the clamped level at the ADCLP timing becomes a reference (CLPCAP at the figure

below), and the ADIN input dynamic range is +1.0 V (TYP.) from the reference level.

**ADIN Signal Input Level**

#### **POWER DOWN MODE**

The power down mode can be set either by register setting or STBYN pin.

If one of them is set, the IR3Y48A1 powers down. ("OR" logic)

#### **MONITOR OUTPUT**

By setting the register [Mode (2) Register D1 & D0], the signal from MONOUT is selectable. Alternatives

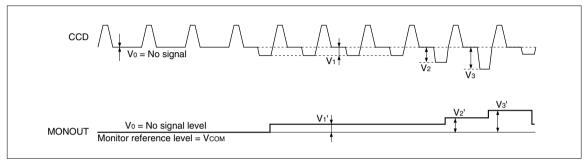

are OFF, CDS output, PGA output, or REFIN/CCDIN output. Note that the gain of the MONOUT pin is fixed to 0 dB regardless the setting of gain control register when the CDS output is selected. The output level of MONOUT is shown below. The MONOUT level becomes Vcom at zero reference level. The signals are output in reverse for the CCD input.

**Monitor Output Level**

#### **POLARITY INVERSION**

The following input polarities can be inverted by register setting:

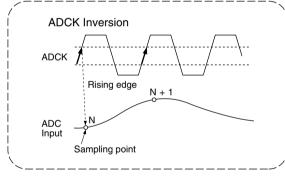

① ADCK (A/D converter sampling clock)

[Mode (1) Register D6]

- ② SHR and SHD (CDS sampling clock)

- [Mode (2) Register D<sub>3</sub> & D<sub>2</sub>]

- ③ BLK, OBP, CCDCLP and ADCLP (Enable controls)

[Mode (2) Register D3 & D2]

#### **Power Control**

Usually, make the power control register (Mode (1) Register D3) "1" to select low power mode.

The default setting of this register is "1".

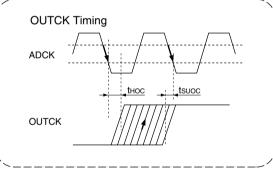

### **Data Output Clock**

The ADCK input or the OUTCK input is selectable as an ADC data output clock.

### **General Notice for Power Supply**

It is recommended to supply power to both AVDD and DVDD from a single regulator.

(Keep the absolute maximum rating; DVDD  $\leq$  (AVDD + 0.3 V) even at the power-up or the power-down sequence.)

Refer to "APPLICATION CIRCUIT EXAMPLE" for power supply decouplings.

#### Serial Interface Circuit

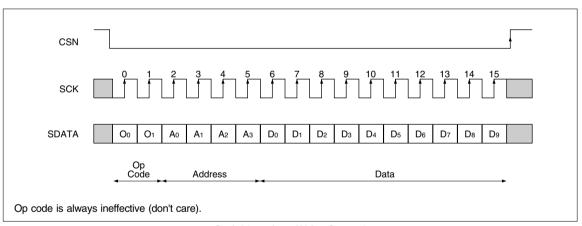

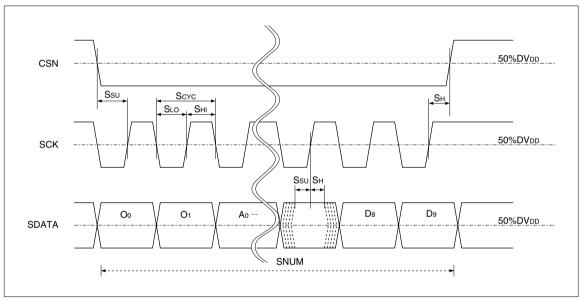

The internal registers of IR3Y48A1 are controlled by the 3-wire serial interface. The data is a 16-bit-length serial data that consists of a 2-bit operation code, a 4-bit address, and a 10-bit data. The each bit is fetched at the rising edge of the SCK input and the data is executed at the rising edge of the CSN input. When not access, make the CSN input high.

It is prohibited to write to a non-defined address. When a data length is below 16-bit, the data is not executed.

**Serial Interface Write Control**

# **Registers**

The IR3Y48A1 has 10-bit x 7 registers to control its operations. Two of the seven registers are used for

the LSI testing.

All registers are write only. The serial registers are written by the serial interface.

#### Register Map

| R/W | Α | DDI        | RES | s | REGISTER NAME     | MAJOR FUNCTIONS [DATA]                                           |

|-----|---|------------|-----|---|-------------------|------------------------------------------------------------------|

|     |   | <b>A</b> 2 | _   | _ |                   |                                                                  |

| w   |   |            |     | _ | Maria (4)         | DOUT timing control/OUTCK polarity/ADCK polarity/ADIN            |

| **  | 0 | 0          | 0   | 0 | Mode (1)          | connection/Power control/ADC output/Black level reset/Power down |

| w   |   |            |     | 1 | Mada (0)          | Clamp current/ADIN clamp/Clamp target/ S/H, enable logic/Monitor |

| vv  | 0 | 0          | 0   | 1 | Mode (2)          | selection                                                        |

| W   | 0 | 0          | 1   | 0 | Mode (3)/CDS gain | CDS gain control/Black loop gain boost/Boost period              |

| W   | 0 | 0          | 1   | 1 | PGA gain          | PGA gain                                                         |

| W   | 0 | 1          | 0   | 0 | Black level       | ADC code at black level (1 LSB step)                             |

| W   | 1 | 0          | 0   | 0 | Test (1)          | Test mode (1) (ADIN coupling mode)                               |

| W   | 1 | 0          | 0   | 1 | Test (2)          | Test mode (2)                                                    |

1. Register name

Mode (1)

2. Register address [Write]

A3 A2 A1 A0 0 0 0 0

# 3. Register bit assignment

|                     | D9 | D8  | D7  | D6  | D <sub>5</sub> | D4 | Дз  | D2  | D1     | Do  |

|---------------------|----|-----|-----|-----|----------------|----|-----|-----|--------|-----|

| Default             | Х  | 0   | 0   | 0   | 0              | 0  | 0   | 0   | 0      | 0   |

| Functions           |    |     |     |     |                |    |     |     |        |     |

| DOUT timing control |    | <-> |     |     |                |    |     |     |        |     |

| OUTCK polarity      |    |     | <-> |     |                |    |     |     |        |     |

| ADCK polarity       |    |     |     | <-> |                |    |     |     |        |     |

| ADIN connection     |    |     |     |     | <              | >  |     |     |        |     |

| Power control       |    |     |     |     |                |    | <-> |     |        |     |

| ADC output          |    |     |     |     |                |    |     | <-> |        |     |

| Black level reset   |    |     |     |     |                |    |     |     | \<br>\ |     |

| Power down          |    |     |     |     |                |    |     |     |        | <-> |

#### 4. Register operations

|                     |    |    |    | CC             | TNC            | RO | LS |    |    |    | OPERATIONS                             | NOTE |

|---------------------|----|----|----|----------------|----------------|----|----|----|----|----|----------------------------------------|------|

|                     | D9 | D8 | D7 | D <sub>6</sub> | D <sub>5</sub> | D4 | Dз | D2 | D1 | Do | OPERATIONS                             | NOTE |

| DOUT timing control |    | 0  |    |                |                |    |    |    |    |    | DOUT synchronizes to ADCK              |      |

|                     |    | 1  |    |                |                |    |    |    |    |    | DOUT synchronizes to OUTCK             |      |

| OUTCK polarity      |    |    | 0  |                |                |    |    |    |    |    | DOUT changes at OUTCK rising edge      | 1    |

|                     |    |    | 1  |                |                |    |    |    |    |    | DOUT changes at OUTCK falling edge     | 1    |

| ADCK polarity       |    |    |    | 0              |                |    |    |    |    |    | Normal operation as timing chart       |      |

|                     |    |    |    | 1              |                |    |    |    |    |    | ADCK clock inversion                   |      |

| ADIN connection     |    |    |    |                | 0              | 0  |    |    |    |    | ADIN function OFF                      |      |

|                     |    |    |    |                | 0              | 1  |    |    |    |    | ADIN signal to PGA                     |      |

|                     |    |    |    |                | 1              | Х  |    |    |    |    | ADIN signal to ADC                     |      |

| Power control       |    |    |    |                |                |    | 0  |    |    |    | Not recommended                        |      |

|                     |    |    |    |                |                |    | 1  |    |    |    | Low power                              | 2    |

| ADC output          |    |    |    |                |                |    |    | 0  |    |    | Normal operation [ADC data output]     |      |

|                     |    |    |    |                |                |    |    | 1  |    |    | ADC output High-Z [or logic of STBYN]  | 3    |

| Black level reset   |    |    |    |                |                |    |    |    | 0  |    | Normal operation                       |      |

|                     |    |    |    |                |                |    |    |    | 1  |    | Black level reset [or logic of RESETN] | 4    |

| Power down          |    |    |    |                |                |    |    |    |    | 0  | Normal operation                       |      |

|                     |    |    |    |                |                |    |    |    |    | 1  | Power down [or logic of STBYN]         |      |

#### NOTES:

- 1. DOUT edge control is effective when D8 = 1 (DOUT synchronizes to OUTCK).

- 2. Power control bit (D3) must be "1" to operate as specified value.

The default value is "1" (low power).

ADC output is set to high impedance if one of the following case is true.

Case 1 : Set "ADC output" bit to "1". Case 2 : Set STBYN pin to low. Case 3 : Set "Power down" bit to "1". X : Don't care

4. Black level integral CAP [OBCAP] is discharged if the following case is true.

Case 1 : Set "Black level reset" bit to "1". Case 2 : Set RESETN pin to low.

Mode (2)

2. Register address [Write]

A3 A2 A1 A0 0 0 0 1

# 3. Register bit assignment

|                   | D9 | D8 | D7  | D <sub>6</sub> | D <sub>5</sub> | D4 | Dз | D2 | D1 | Do |

|-------------------|----|----|-----|----------------|----------------|----|----|----|----|----|

| Default           | Х  | Х  | 0   | 0              | 0              | 0  | 0  | 0  | 0  | 0  |

| Functions         |    |    |     |                |                |    |    |    |    |    |

| Clamp current     |    |    | <-> |                |                |    |    |    |    |    |

| ADIN clamp        |    |    |     | <->            |                |    |    |    |    |    |

| Clamp target      |    |    |     |                | <              | >  |    |    |    |    |

| S/H, enable logic |    |    |     |                |                |    | <> |    |    |    |

| Monitor selection |    |    |     |                |                |    |    |    | <  | >  |

X : Don't care

### 4. Register operations

|                   |    |    |    | CC | TNC            | RO | LS |    |    |    | ODEDATIONS                                 | NOTE |  |

|-------------------|----|----|----|----|----------------|----|----|----|----|----|--------------------------------------------|------|--|

|                   | D9 | D8 | D7 | D6 | D <sub>5</sub> | D4 | Dз | D2 | D1 | Do | OPERATIONS                                 | NOTE |  |

| Clamp current     |    |    | 0  |    |                |    |    |    |    |    | Normal clamp (±50 μA)                      |      |  |

|                   |    |    | 1  |    |                |    |    |    |    |    | Fast clamp (±100 μA)                       |      |  |

| ADIN clamp        |    |    |    | 0  |                |    |    |    |    |    | Clamp operation active for ADIN            |      |  |

|                   |    |    |    | 1  |                |    |    |    |    |    | No clamp for ADIN                          |      |  |

| Clamp target      |    |    |    |    | 0              | 0  |    |    |    |    | Normal mode [Clamp both REFIN and CCDIN]   |      |  |

|                   |    |    |    |    | 0              | 1  |    |    |    |    | Clamp REFIN only                           |      |  |

|                   |    |    |    |    | 1              | 0  |    |    |    |    | Clamp CCDIN only                           |      |  |

|                   |    |    |    |    | 1              | 1  |    |    |    |    | Clamp OFF                                  |      |  |

| S/H, enable logic |    |    |    |    |                |    | 0  | 0  |    |    | Normal operation as timing chart           |      |  |

|                   |    |    |    |    |                |    | 0  | 1  |    |    | S/H control polarity inversion             | 1    |  |

|                   |    |    |    |    |                |    | 1  | 0  |    |    | Enable control polarity inversion          | 2    |  |

|                   |    |    |    |    |                |    | 1  | 1  |    |    | Both of S/H and enable inversion           |      |  |

| Monitor selection |    |    |    |    |                |    |    |    | 0  | 0  | Monitor OFF                                |      |  |

|                   |    |    |    |    |                |    |    |    | 0  | 1  | CDS signal to monitor                      | 3    |  |

|                   |    |    |    |    |                |    |    |    | 1  | 0  | PGA output monitor                         | 4    |  |

|                   |    |    |    |    |                |    |    |    | 1  | 1  | 1 Output REFIN and CCDIN (for calibration) |      |  |

#### **NOTES:**

- 1. The S/H signals are SHR and SHD.

- 2. The enable controls are BLK, OBP, CCDCLP, and ADCLP.

- 3. At this mode, monitor output gain = 0 dB regardless of CDS gain.

- 4. At this mode, monitor output depends on CDS gain.

Mode (3)

Register address [Write]

A3 A2 A1 A0 0 0 1 0

#### 3. Register bit assignment

|                       | D9 | D8 | D7 | D <sub>6</sub> | D <sub>5</sub> | D4 | Dз  | D2 | D1 | Do |

|-----------------------|----|----|----|----------------|----------------|----|-----|----|----|----|

| Default               | Х  | Х  | Х  | Х              | 0              | 0  | 0   | 0  | 0  | 0  |

| CDS gain control      |    |    |    |                | <              | >  |     |    |    |    |

| Black loop gain boost |    |    |    |                |                |    | <-> |    |    |    |

| Boost period          |    |    |    |                |                |    |     | <  |    | -> |

X : Don't care

#### 4. Register operations

|                       |    | CONTROLS  D9 D8 D7 D6 D5 D4 D3 D2 D1 D0 |    |                |                |    |    |    |    |    | OPERATIONS                 | NOTE |

|-----------------------|----|-----------------------------------------|----|----------------|----------------|----|----|----|----|----|----------------------------|------|

|                       | D9 | D8                                      | D7 | D <sub>6</sub> | D <sub>5</sub> | D4 | Дз | D2 | D1 | Do | OPERATIONS                 | NOTE |

| CDS gain control      |    |                                         |    |                | 0              | 0  |    |    |    |    | CDS gain = 0 dB            |      |

|                       |    |                                         |    |                | 0              | 1  |    |    |    |    | CDS gain = +6.02 dB        |      |

|                       |    |                                         |    |                | 1              | 0  |    |    |    |    | CDS gain = +12.04 dB       |      |

|                       |    |                                         |    |                | 1              | 1  |    |    |    |    | CDS gain = $-1.94$ dB      |      |

| Black loop gain boost |    |                                         |    |                |                |    | 0  |    |    |    | Boost control ON           | 1    |

|                       |    |                                         |    |                |                |    | 1  |    |    |    | Always high gain           | 2    |

| Boost period          |    |                                         |    |                |                |    |    | 0  | 0  | 0  | Always low gain            | 3    |

|                       |    |                                         |    |                |                |    |    | 0  | 0  | 1  | High gain for 1 OBP pulse  | 1, 3 |

|                       |    |                                         |    |                |                |    |    | 0  | 1  | 0  | High gain for 2 OBP pulses | 1, 3 |

|                       |    |                                         |    |                |                |    |    | 0  | 1  | 1  | High gain for 3 OBP pulses | 1, 3 |

|                       |    |                                         |    |                |                |    |    | 1  | 0  | 0  | High gain for 4 OBP pulses | 1, 3 |

|                       |    |                                         |    |                |                |    |    | 1  | 0  | 1  | High gain for 5 OBP pulses | 1, 3 |

|                       |    |                                         |    |                |                |    |    | 1  | 1  | 0  | High gain for 6 OBP pulses | 1, 3 |

|                       |    |                                         |    |                |                |    |    | 1  | 1  | 1  | High gain for 7 OBP pulses | 1, 3 |

#### NOTES:

- Black loop settling gain is boosted [speed up] for defined period.

Gain is boosted n OBP pulse(s) after rising edge of CSN [SIO data write].

Boosted period n (1 to 7 pulses) is determined by "boost period" (D2...Do).

After n OBP pulse(s), black loop gain returns automatically to low gain.

- 2. Black loop settling is always high gain [boosted].

- 3. "Boost period" register is effective only when  $D_3 = 1$ .

PGA gain

2. Register address [Write]

| Аз | <b>A</b> 2 | <b>A</b> 1 | Αo |

|----|------------|------------|----|

| 0  | 0          | 1          | 1  |

# 3. Register bit assignment

|           | D9 | D8 | D7 | D <sub>6</sub> | D <sub>5</sub> | D4 | Dз | D2 | D1 | Do |

|-----------|----|----|----|----------------|----------------|----|----|----|----|----|

| Default   | Х  | 0  | 0  | 0              | 0              | 0  | 0  | 0  | 0  | 0  |

| Functions |    |    |    |                |                |    |    |    |    |    |

| PGA gain  |    | <- |    |                |                |    |    |    |    | -> |

X : Don't care

# 4. Register operations

|          |    |    |    | CC             | TNC            | RO | LS |    |    |                | DECIMAL | шту | PGA       |

|----------|----|----|----|----------------|----------------|----|----|----|----|----------------|---------|-----|-----------|

|          | D9 | D8 | D7 | D <sub>6</sub> | D <sub>5</sub> | D4 | Дз | D2 | D1 | D <sub>0</sub> | DECIMAL | HEX | GAIN (dB) |

| PGA gain |    | 0  | 0  | 0              | 0              | 0  | 0  | 0  | 0  | 0              | 0       | 0   | 0.000     |

|          |    | 0  | 0  | 0              | 0              | 0  | 0  | 0  | 0  | 1              | 1       | 1   | 0.047     |

|          |    | 0  | 0  | 0              | 0              | 0  | 0  | 0  | 1  | 0              | 2       | 2   | 0.094     |

|          |    | 0  | 0  | 0              | 0              | 0  | 0  | 0  | 1  | 1              | 3       | 3   | 0.141     |

|          |    | 0  | 0  | 0              | 0              | 0  | 0  | 1  | 0  | 0              | 4       | 4   | 0.188     |

|          |    |    |    |                |                |    |    |    |    |                |         |     |           |

|          |    | 0  | 0  | 0              | 1              | 1  | 1  | 1  | 1  | 0              | 62      | 3E  | 2.916     |

|          |    | 0  | 0  | 0              | 1              | 1  | 1  | 1  | 1  | 1              | 63      | 3F  | 2.963     |

|          |    | 0  | 0  | 1              | 0              | 0  | 0  | 0  | 0  | 0              | 64      | 40  | 3.010     |

|          |    | 0  | 0  | 1              | 0              | 0  | 0  | 0  | 0  | 1              | 65      | 41  | 3.057     |

|          |    |    |    |                |                |    |    |    |    |                |         |     |           |

|          |    | 0  | 0  | 1              | 1              | 1  | 1  | 1  | 1  | 1              | 127     | 7F  | 5.973     |

|          |    | 0  | 1  | 0              | 0              | 0  | 0  | 0  | 0  | 0              | 128     | 80  | 6.020     |

|          |    | 0  | 1  | 0              | 0              | 0  | 0  | 0  | 0  | 1              | 129     | 81  | 6.067     |

|          |    |    |    |                |                |    |    |    |    |                |         |     |           |

|          |    | 0  | 1  | 1              | 0              | 0  | 0  | 0  | 0  | 0              | 192     | C0  | 9.030     |

|          |    |    |    |                |                |    |    |    |    |                |         |     |           |

|          |    | 0  | 1  | 1              | 1              | 1  | 1  | 1  | 1  | 1              | 255     | FF  | 11.993    |

|          |    | 1  | 0  | 0              | 0              | 0  | 0  | 0  | 0  | 0              | 256     | 100 | 12.040    |

|          |    | 1  | 0  | 0              | 0              | 0  | 0  | 0  | 0  | 1              | 257     | 101 | 12.087    |

|          |    |    |    |                | •••            |    |    |    |    |                |         |     |           |

|          |    | 1  | 0  | 1              | 0              | 0  | 0  | 0  | 0  | 0              | 320     | 140 | 15.050    |

|          |    |    |    |                | •••            |    |    |    |    |                |         |     |           |

|          |    | 1  | 0  | 1              | 1              | 1  | 1  | 1  | 1  | 1              | 383     | 17F | 18.013    |

|          |    | 1  | 1  | 0              | 0              | 0  | 0  | 0  | 0  | 0              | 384     | 180 | 18.060    |

|          |    | 1  | 1  | 0              | 0              | 0  | 0  | 0  | 0  | 1              | 385     | 181 | 18.107    |

|          |    |    |    |                |                |    |    |    |    |                |         |     |           |

|          |    | 1  | 1  | 1              | 0              | 0  | 0  | 0  | 0  | 0              | 448     | 1C0 | 21.070    |

|          |    |    |    |                |                |    |    |    |    |                |         |     |           |

|          |    | 1  | 1  | 1              | 1              | 1  | 1  | 1  | 1  | 0              | 510     | 1FE | 23.986    |

|          |    | 1  | 1  | 1              | 1              | 1  | 1  | 1  | 1  | 1              | 511     | 1FF | 24.033    |

Black level

2. Register address [Write]

| Аз | <b>A</b> 2 | <b>A</b> 1 | Αo |

|----|------------|------------|----|

| 0  | 1          | 0          | 0  |

# 3. Register bit assignment

|             | D9 | D8 | D7 | D <sub>6</sub> | D <sub>5</sub> | D4 | Dз | D2 | D1 | Do |

|-------------|----|----|----|----------------|----------------|----|----|----|----|----|

| Default     | Х  | Х  | Х  | 1              | 0              | 0  | 0  | 0  | 0  | 0  |

| Functions   |    |    |    |                |                |    |    |    |    |    |

| Black level |    |    |    | <              |                |    |    |    |    | >  |

X : Don't care

### 4. Register operations

|             | OP | ER/ | ATIO | NS             | [AD        | C C | ODE | : BI           | NAI | RY] | BLACK     | CODE      | NOTE |

|-------------|----|-----|------|----------------|------------|-----|-----|----------------|-----|-----|-----------|-----------|------|

|             | В9 | В8  | В7   | B <sub>6</sub> | <b>B</b> 5 | В4  | Вз  | B <sub>2</sub> | B1  | Во  | DECIMAL   | HEX       | NOTE |

| Black level |    |     |      | 0              | 0          | 0   | 0   | 0              | 0   | 0   | FORBIDDEN | FORBIDDEN |      |

|             |    |     |      | 0              | 0          | 0   | 0   | 0              | 0   | 1   | 1         | 1         | 1    |

|             |    |     |      |                |            |     | ••• |                |     |     |           |           | 1    |

|             |    |     |      | 0              | 0          | 0   | 1   | 1              | 1   | 1   | 15        | F         | 1    |

|             |    |     |      | 0              | 0          | 1   | 0   | 0              | 0   | 0   | 16        | 10        |      |

|             |    |     |      | 0              | 0          | 1   | 0   | 0              | 0   | 1   | 17        | 11        |      |

|             |    |     |      | 0              | 0          | 1   | 0   | 0              | 1   | 0   | 18        | 12        |      |

|             |    |     |      | 0              | 0          | 1   | 0   | 0              | 1   | 1   | 19        | 13        |      |

|             |    |     |      |                |            |     | ••• |                |     |     |           |           |      |

|             |    |     |      | 0              | 1          | 0   | 0   | 0              | 0   | 0   | 32        | 20        |      |

|             |    |     |      |                |            |     | ••• |                |     |     |           |           |      |

|             |    |     |      | 1              | 0          | 0   | 0   | 0              | 0   | 0   | 64        | 40        |      |

|             |    |     |      |                |            |     | ••• |                |     |     |           |           |      |

|             |    |     |      | 1              | 1          | 1   | 1   | 1              | 0   | 0   | 124       | 7C        |      |

|             |    |     |      | 1              | 1          | 1   | 1   | 1              | 0   | 1   | 125       | 7D        |      |

|             |    |     |      | 1              | 1          | 1   | 1   | 1              | 1   | 0   | 126       | 7E        |      |

|             |    |     |      | 1              | 1          | 1   | 1   | 1              | 1   | 1   | 127       | 7F        |      |

# NOTE:

1. Codes 1 to 15 are available but not recommended. Black calibration period is specified under 15 < code < 128.

Test (1)

2. Register address [Write]

| Аз | <b>A</b> 2 | <b>A</b> 1 | Αo |

|----|------------|------------|----|

| 1  | 0          | 0          | 0  |

3. Register bit assignment

|                | D9 | D8 | D7 | D <sub>6</sub> | D <sub>5</sub> | D4 | Dз | D2 | D1 | Do |

|----------------|----|----|----|----------------|----------------|----|----|----|----|----|

| Default        | Х  | Х  | Х  | 0              | 0              | 0  | 0  | 0  | 0  | 0  |

| Functions      |    |    |    |                |                |    |    |    |    |    |

| ADIN test mode |    |    |    | <->            |                |    |    |    |    |    |

NOTE:

X : Don't care

D<sub>5</sub> to D<sub>0</sub> must always be "0".

4. Register operations

|                |    |    |    | CC | TNC            | RO | LS |    |    |    | OPERATIONS                         |

|----------------|----|----|----|----|----------------|----|----|----|----|----|------------------------------------|

|                | D9 | D8 | D7 | D6 | D <sub>5</sub> | D4 | Dз | D2 | D1 | Do | OPERATIONS                         |

| ADIN test mode |    |    |    | 0  |                |    |    |    |    |    | Normal operation                   |

|                |    |    |    | 1  |                |    |    |    |    |    | Vсом centered ADIN for AC coupling |